So how do you produce a usable, somewhat analog signal out of a purely digital device? Well it’s actually simple; use a R-2R ladder and a bunch of digital pins. Basically we’re turning a dearth of extremely high speed digital IO pins into one high-resolution analog output. Oh, also necessary for this circuit (go ahead and crack out the protoboard and soldering iron) is 3 matched resistor per bit of resolution; so in our case, 48.

Fun! Here’s a diagram. So how’s it work? When we drive our 16 outputs with digital logic, each pin has half the voltage range of its leftwards neighbor — due to it being a stacked voltage divider. This is exactly how you convert from binary to decimal; each digit has twice the value of one neighbor, and half that of the other (discounting the Most and Least Significant Bits) so we can convert 1s and 0s into a wide numeric range of values.

This is probably confusing: I know how it works, and I just confused myself. For a *much* better explanation, refer to this previous post of mine.

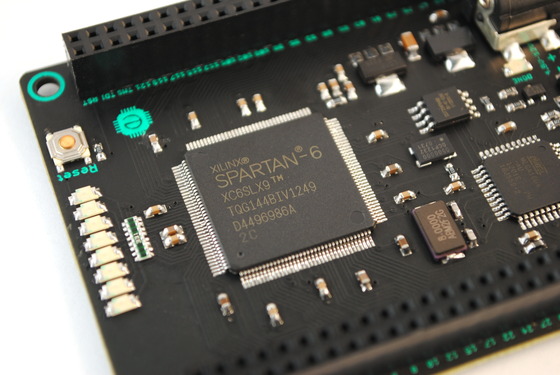

We’ve got a circuit, we know conceptually how it works, how do we make it do? Make…make it do right? This is where my brain started screeching to a halt. Hell, I must be driving with the E-brake on, because this is actually super easy, and explaining why helps to understand VHDL/Verilog.

Firstly, in programming languages, things happen sequentially: A, then B, then conditionally C, for example. In Hardware Description Languages, things happen simultaneously: A <= a and B <= b and C <= c all happen simultaneously. Secondly, all of our analog values we’d want to output, such as 62101 is actually represented in a variable, described thusly:

wire [15:0] our_var

It’s actual designation in the chip is in the form 0b1111001010010101.

This means all we have to do to convert our digital data to our analog output at full clock speed is this:

always @(*) begin

pin15 <= our_var[15]

pin14 <= our_var[14]

...

pin1 <= our_var[1]

pin0 <= our_var[0]

end

These all update at the same time, and our output is produced thusly. So, I’ve been dismissing the most major disadvantage? Speed. Lets say we want to make a 16b sine wave. Our speed is limited to f_clk/number_of_levels. So FM is out of the question with this particular implementation (I’m not ruling it out completely, let me know if you know more than I do) but it’s the perfect speed for audio applications.

With a 350MHz DCM, and using 16,384 distinct levels, I can generate a f_max of around 21kHz, well above the range of human hearing. So let me work on getting that code finished, and I’ll return tomorrow. I’ve got my wheels pointed towards the curb, and my E-brake on, and I need a break for the night.